WDC 65816 - MIRKOSOFT

All what your computer needs...

Main menu:

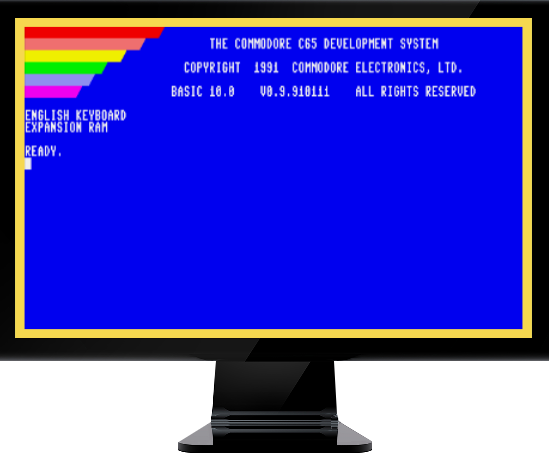

W65C816S is inside CMD SuperCPU for Commodore 64 and Commodore 128 and CPU of Apple IIGS

Western Design Center 65816

65K 8/16-bit CPU

Max. clock speed:

14MHz

downclocked to 2,8MHz in Apple IIGS

overclocked to 20MHz in CMD SuperCPU

Fully static CMOS design for low power consumption (300µA at 1MHz) and increased noise immunity

Wide operating voltage range: 1.8V ± 5%, 2.5V ± 5%, 3.0V ± 5%, 3.3V ± 10%, 5.0V ± 5% for use with varying voltage peripherals

Wide operating frequency range, using a single-phase clock source

Emulation mode allows software compatibility with the 65C02, excepting undocumented opcodes

24-bit memory addressing provides access to 16MB of memory space

16-bit ALU, accumulator (A), stack pointer (SP), and index registers (X and Y)

16-bit Direct Page register (D)

8-bit Data Bank (DB) and Program Bank (PB) registers, generating bits 16-23 of 24-bit data and code addresses

Valid Data Address (VDA) and Valid Program Address (VPA) outputs for dual cache and cycle steal DMA implementation

Vector Pull (VPB) output to indicate when an interrupt vector is being addressed

Abort (ABORTB) input and associated vector supports processor repairs of bus error conditions, such as page faults and memory access violations

Separate program and data bank registers allow program segmentation or 16MB linear addressing (data only)

Direct register and stack relative addressing provides capability for reentrant, recursive and re-locatable programming

24 addressing modes - 13 original 6502 modes with 92 instructions using 256 opcodes, including most new opcodes implemented in the 65C02

Block-copy instructions, allowing rapid copying of data structures from one area of RAM to another with minimal code

Wait-for-Interrupt (WAI) and Stop-the-Clock (STP) instructions further reduce power consumption, decrease interrupt latency and allows synchronization with external events

Co-Processor (COP) instruction with associated vector supports co-processor configurations, e.g., floating point processors

Reserved "escape" WDM instruction for future two-byte opcodes and a link to future designs. (WDM is the initials of W65C816S designer William D. Mensch)

W65C816S (also 65C816 or 65816) is a 16-bit microprocessor (MPU) developed and sold by the Western Design Center (WDC). Introduced in 1983, the W65C816S is an enhanced version of the WDC 65C02 8-bit MPU, itself a CMOS enhancement of the venerable MOS Technology 6502 NMOS MPU. The 65 in the part's designation comes from its 65C02 compatibility mode, and the 816 signifies that the MPU has selectable 8-bit and 16-bit register sizes. In addition to the availability of 16 bit registers, the W65C816S features extended memory addressing to 24-bits, supporting up to 16 megabytes of memory, an enhanced instruction set, and a 16 bit stack pointer, as well as several new electrical signals for improved system hardware management. At reset the W65C816S starts in "emulation mode" meaning it essentially behaves as a 65C02. Following reset, the W65C816S may be switched to "native mode" with a two instruction sequence, causing it to enable all enhanced features, yet still maintain a substantial degree of backward compatibility with most 65C02 software. However, unlike the PDIP40 version of the 65C02, which is a pin-compatible replacement for its NMOS ancestor, PDIP40 W65C816S is not pin-compatible with any other 6502 family MPU.